Если вы не готовы читать предыдущий материал, и вникать в код - то и эту публикацию читать не стоит пожалуй. Прошу прощения. Без понимания предыдущего кода и алгоритма, что по ссылке ниже, и блок схемы - это чтение будет бесполезным. Изменяю сложность публикации и прошу прощения. Сразу вставляю ссылку на материал, с которым стоит ознакомиться.

Небольшой ликбез для чатботов под спойлером.

Hidden text

Один "грамотный" чатбот написал что диаграмма ничего не передаёт кроме фантазий. А если-бы он был немного грамотнее - у него оных не возникло-бы, так как передаёт автор, с помощью текста и графических средств, функция которых отображение графической информации, никаких экстрасенсорных и телепатических способностей ни у автора, ни у применяемых им средств - нету и ранее не наблюдалось тоже.

На самом деле, ввиду прошлой публикации (последствия которой я постараюсь исправить, так как наверное многие решили что это плод воображения - новая архитектура) - препроцессора, так как рассматриваю процессор и пост процессор. Для того, чтобы понять ход мыслей лучше, и то, что всё это не фантазии, а результат работы - стоит ознакомиться с этой предыдущей публикацией (второй раз - просто не всем сразу понятно, и они продолжают писать комментарии не читая текста публикации), она не сильно длинная - но время отнимет, хоть и не сильно сложная.

Ознакомившись с ней станет понятно что имеется ввиду под модификациями кода (смена формул и выключение строк кода в рантайме), под модификациями кода подразумевается просто включение и выключение исполняемых команд, кода. Изначально мной предполагалось, что кэш мостов будет состоять из параллельных частей, и скорее всего в такой архитектуре конвейера он должен будет и обеспечивать работу меток и указателей (но сейчас не про них). В каких-то публикациях мне сделали замечания что мало графики и рисунков (вроде как про поляризацию для машинного зрения), но как можно увидеть из публикации по ссылке выше - оказалось достаточно одной блок-схемы чтобы отполировать и видоизменить весь код, и даже до той степени, чтобы задуматься о новой архитектуре.

Архитектура препроцессора (это нечто вроде ядра GPU), и что для неё нужно.

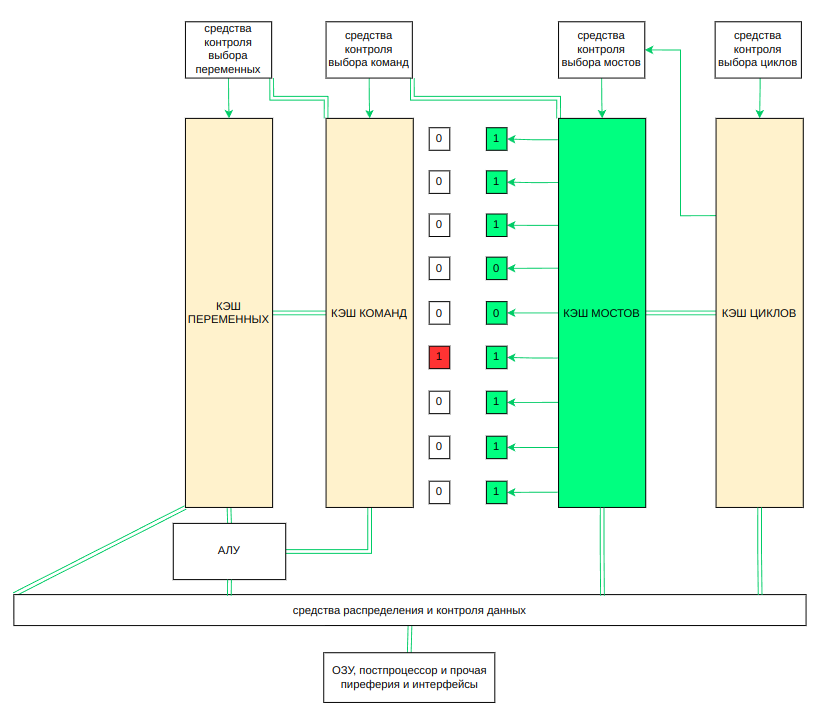

Как мне представвляется нужны новые типы данных для работы такого конвейера, а именно обособить циклы в отдельный тип и создать для них свой Кеш. Острая необходимость этого видна из публикации по ссылке выше, кто не любит читать - прошу не ругать меня, так как пишу не про плоды воображения, а про результаты работ и выводы. Идея создания кэша мостов пришла при анализе того-же кода и при очевидной необходимости модификации кода в рантайме. Затем должны идти кэш команд и следом кэш переменных, перед АЛУ. Код выполняемый на препроцессоре должен компилироваться под него, и при загрузке в препроцессор распределяться по трём кэшам: команд, мостов и циклов. Всё это мной уже было обозримо и схема была при прошлой публикации о архитектуре вычислительной машины. И далее как мной обещалось - были проанализированы формулы (мне пришлось вспоминать, так как писал я их в попыхах и никаких заметок не делал), в них мной ничего интересного обнаружено не было, и всё работает и в таком виде: изначальную формулу закомментировал

// TracerX := x - ( znak*sign(trunc((1+sign(y-trunc(y/(stepsBig+1))*(stepsBig+1)-steps)/2))) + formula1)+1;

TracerX := x - formula1+1;

if (y mod SummSteps)-steps = 0 then TracerX:= TracerX-znak;

if (y mod SummSteps)-steps > 0 then TracerX:= TracerX-znak;Но там ничего не интересно особо. Теперь к самому интересному - процессору без счётчика команд. Эта идея мне пришла сразу, как только от формул я вернулся к схеме конвейера . Представлю немного изменённую схему, так как она уже с элементами под описание конвейера без счётчика команд.

То-есть, на схематичном изображении представлены, от второго блока и выше, конвейер (ядро) препроцессора. Согласно прошлой публикации - роль аналога CPU будет выполнять постпроцессор. И препроцессор, и постпроцессор - в данной архитектуре являются физическими процессорами (в IT препроцессор - программный продукт).

Что тут изображено по порядку кэш циклов - на нём задерживаться не стоит, просто стоит отметить что циклы тут обособлены в некий тип и у них свой кэш. Это сделано не просто так, а для того, чтобы средства контроля, пока выполняется команда в следующих справа на лево кэшах, при возможности исполняли свою команду над кэшом цикла и переводили его в режим ожидания завершения работы со следующими кэшами, условно принцип - "прикоснись и иди дальше", или нечто вроде работы некоторого многозвенного автомата. Кэш мостов - это самая интересная часть, на мой взгляд, так как именно она открывает возможность реализации процессора без счётчика команд, впрочем на этот кэш и тип мной изначально возлагались большие надежды, так как с его помощью планировалось проводить в рантайме небольшие модификации кода, но идеи такой хорошей как сейчас тогда не было. Часть кэша мостов прикреплена к кэшу команд на схеме - зелёные ячейки, биты, содержащие или нули или единицы. Такого-же размера ячейки справа - биты выполнения кода. На схеме красная ячейка с единицей - представляет адрес кэша команд, с которого читается команда. Далее текстовое изложение усложняется, как это должно работать после чтения команда кэш команд должен перейти к следующему адресу, для этого по линии битов мостов пускается сигнал, и если в следующем адресе бит мостов содержит единицу, то она (наверное средством типа месфета, тут я полный нуб и мне многое предстоит изучить) аппаратно блокирует прохождение сигнала дальше по линии битов мостов, если ноль - то свободно пропускает, не активируя текущий его адрес для чтения (не записывая в него единицу), как только будет достигнут бит мостов с единицей - в него перезапишется бит выполнения в единицу, а в изначальном он выставится в ноль. Конечно в электронике, в отличии от алгоритмов и способов, я новичок, и скорых результатов и публикаций от меня не будет. Реализация, как новичку мне представляется не сложной - две дорожки с минимальными средствами типа месфета (это не точно, поскольку тут я полный нуб, но не совсем), конечно я не знаю насколько просто это исполнить на FPGA, ну и разумеется две битовые ячейки на каждый адрес кэша команд: бит выполнения и бит мостов. Модификации выполняемой программы планируется выполнять посредством команд установки состояния битов мостов. Тут уж извините за мою хромую терминологию - обещаю всё подтянуть к следующей, не скорой, публикации , с уже какими-то результатами. Изначально, от идеи "поляризации машинного зрения", мною решалась задача поиска наиболее быстрых способов, алгоритмов, это сохранилось и при написании генератора карт (в рамках проекта), этого - же эффекта мной ожидается и от данной архитектуры - не нужно будет искать адрес в кэше команд, переход к следующему будет совершаться аппаратно и полностью автоматически. При желании можно сделать ядро многорежимным, или при необходимости, этот опыт кэша мостов ( без счётчика команд ) можно будет применить и к остальным кэшам процессора. Все кэшы, предполагается, будут доступны программисту для манипуляций над ними посредством команд.

Если у кого-то будет желание мне помочь в освоении новых знаний, для продолжении работы, то предоставлю информацию: ОС Ubunta 22.04 , из полезных программ - Qucs Spice, её только вот-вот начинаю осваивать в краткий прайм-тайм между временем уходящим на основную работу и сном, минус какие-то обычные бытовые повседневные дела. Просто был человек, которому вроде не безынтересно, эта информация больше для него, ну плюс виртуал бокс, но это может +и вообще не понадобится. В рамках проекта не откажусь от любой помощи. Не знаю как вам, а мной надежда не была потеряна десятилетиями (именно решение задачи машинного зрения мной было обозначено как для своего пути для создания AI, ну правда вот и до архитектур дошло, после алгоритмов). Прошу сильно не ругать - ничего чужого не трогаю, все наработки и работы - чисто собственные, поэтому и продолжаю идти своим путём. Если кто-то считает что это вторжение с моей стороны в его сферу - это его заблуждение, так как сфера его не является, а является результатом работы поколений и умов, а патенты на изобретательскую деятельность ещё не изобрели, да и вряд-ли это случится. И кстати повторюсь на всякий случай (многие не внимательно читают) - всё это продолжение работы: этап, анализ, продолжение; этап, анализ, продолжение ... - никаких фантазий. Начало схемы электронной мной уже положено (это конкретно по кэшу команд и мостов), но что-то я стесняюсь его публиковать, ибо нуб.

Пришла литература, начал читать. Вероятно что процессор будет работать в двух режимах или будет полностью аналоговым, на то указывает архитектура на изображении и код из прошлой публикации. Читая литературу я начал понимать что под мой машинный код, а так-же компилируемый лучше подойдёт аналоговый процессор.

Организация работы кэша мостов.

Кэш мостов - некоторый кэш, который обеспечивает работу процессора по обработке кода в кэше команд без счётчика команд. Не считаю нужным делать публикацию по простенькой схеме из цифровой схемотехники, и пользуясь кнопкой редактировать - изменяю текущую публикацию 09.03.2024 от 18.02.2024.

Условно рассматривается кэш мостов, состоящий из пяти ячеек.

Каждый светодиод (программа Logisim) - условно активируемая ячейка памяти, в которой содержится очередная исполняемая команда для процессора. Триггеры Bridge хранят единицу, если команду нужно выполнить в цепи, и ноль - если пропустить. Перед запуском системы кэша мостов нажимается кнопка и в кажде звено цепи кэша, в триггеры Start записываются единицы, после чего в триггер внизу слева схемы записывается единица и он выдаёт постоянный сигнал. При каждом запросе процессора очередной команды - с программируемого тактового генератора подаёётся сигнал на кэш мостов. Триггеры без метки введены для синхронизации. Переход к следующей ячейке с ненулевым значением Bridge осуществляется за один такт (правда схема чисто асинхронная и понятие такта тут применяется только для того, чтобы дать понять то, что её работа синхронизируется с работой процессора), не смотря на количество пропущенных ячеек. Элемент Не введён был для корректировки работы симуляции (без него работало плохо - слишком быстро выполнялись в симуляторе некоторые операции). Позднее триггеры без меток будут обнуляться не с элемента Не, а сигналом с процессора, при работе кэша мостов единицу может содержать тригер без метки только одной ячейки, и обнуляться они будут скорее всего с одного провода.

Всё так-же, по часу в день (в смысле после основной работы), но уже с освоением основ схемотехники и остального. Следующий этап скорее всего - работа с FPGA и Verilog.