Comments 32

Очень интересно. Остался один вопрос: mail.ru-то здесь причем?

+10

«Нельзя просто так взять и...» распараллелить блочное шифрование (AES). В большей части режимов сцепления блоков (OFB, CFB, etc.) входной следующий блок недоступен до окончания шифрования предыдущего.

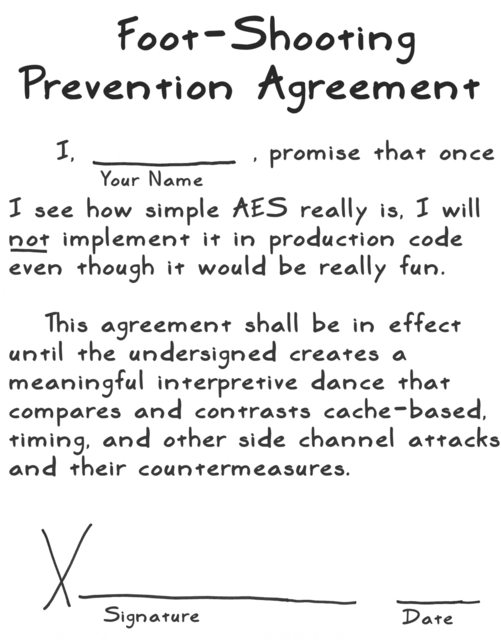

Что ещё раз доказывает — не стоит браться за самостоятельное реализацию «простых и известных алгоритмов», пока не узнаешь хотя бы, что такое timing и вообще side-channel атаки.

Что ещё раз доказывает — не стоит браться за самостоятельное реализацию «простых и известных алгоритмов», пока не узнаешь хотя бы, что такое timing и вообще side-channel атаки.

+2

Я правильно перевел «пока не станцует/объяснит танцем», или там какой-то фразеологизм?

0

Пока не придумает («создаст») имеющий поддающийся [смотрящим] чтению смысл танец. Как-то так.

0

Я думаю тут речь идет о видео где различные алгоритмы сортировки объясняются с помощью танца. Ссылка не плэйлист: www.youtube.com/watch?v=CmPA7zE8mx0&list=PLuE79vNc5Wi6q34LsQcaJ7ISQ8uOyMaL_

+1

Ваше высказывание относительно режимов сцепления блоков (OFB, CFB, etc.) верно, однако ничего не мешает «распараллелить» (читай — конвейеризовать) сами раунды в рамках работы с одним блоком — другим словом: развернуть программный цикл.

0

Если бы речь шла про традиционные процессоры, то на них попытка распараллелить операции в рамках одного раунда привела бы только к замедлению вычислений. Возможно, что подобная «векторизация» вычислений и сработает на описываемой архитектуре. Но что-то мне кажется, что это не то, что имел ввиду автор.

Не уверен, что автор даже разобрался в AES, так как вот такие фразы вызывают большие вопросы:

Тут явно идёт речь не про векторизацию шага внутри раунда, а про попытку раскидать сами шаги между потоками. Насколько я понимаю AES, это невозможно.

Не уверен, что автор даже разобрался в AES, так как вот такие фразы вызывают большие вопросы:

каждый раунд состоит из дискретных шагов. Их тоже можно раскидать, ещё больше увеличив скорость такта

Тут явно идёт речь не про векторизацию шага внутри раунда, а про попытку раскидать сами шаги между потоками. Насколько я понимаю AES, это невозможно.

0

Тут явно идёт речь не про векторизацию шага внутри раунда, а про попытку раскидать сами шаги между потоками.Нет, тут говорится о том, что каждый раунд AES состоит из подшагов (InvShiftRows, InvSubBytes и так далее). Если в каждом такте делать только один подшаг — то количество исполнительных блоков и потребных тактов станет больше, но зато каждый такт станет меньше. Привет Pentium4, короче…

0

UFO just landed and posted this here

Не надо таких статей.

А токаждая домохозяйка любой программист сможет освоить правильный hdl и оставит без хлеба масла и икры честных hdl-дизайнеров.

А то

-4

что никакая цифровая логическая схема не может работать «без тактов». Всегда существуют физические процессы, создающие входные данные. Все эти данные должны быть валидны на старте — в момент, формирующий первый «тик» тактового генератора в схеме.

Утверждение в корне неверно. Используя полный базис логических функций («И», «ИЛИ», «НЕТ»)

можно реализовать любую цифровую логическую схему. Такты вводят для других причин, как то по максимуму исключить «гонки» и проч. Как чел. который делал цифровые логические схемы еще на П416 из за неимения иных элементов, был крайне удивлён что при проектировании FPGA настойчиво навязывают тактирование, даже грешным делом подумал, что это за фуфло такое FPGA которое не может работать без тактов. И как чел. который много десятков лет программирует на всяких емембет и писюках могу сказать, что исенно здесь и выплывают такты, ибо команда за такт или более, а в железе такты как зайцу стоп сигнал.

+2

Просто без тактирования получается многовариантная система с точки зрения гонок и она сложно просчитывается, а с тактами становится понятнее и просчитывается элементарно. Что в общем-то автор и описал.

0

UFO just landed and posted this here

Утверждение, что нельзя взять корень от -1 тоже неверно.

Но почему-то школьникам про это не сразу сообщают. А даже после того как сообщают, большинство успешно обходится вещественными числами всю оставшуюся жизнь.

Но почему-то школьникам про это не сразу сообщают. А даже после того как сообщают, большинство успешно обходится вещественными числами всю оставшуюся жизнь.

0

Асинхронная логика — прошлый век!)

0

> Дело в том, что никакая цифровая логическая схема не может работать «без тактов»

Это не так. Автоматы без памяти и асинхронные схемы вполне работают без «тактов».

Это не так. Автоматы без памяти и асинхронные схемы вполне работают без «тактов».

+5

В начале был такт.

0

Оригинал:

Перевод:

Имеется в виду, что все операции происходили без разделения на шаги (раунды), в одном раунде. Вот зачем такой перевод? Просто бросили бы ссылку на оригинал.

This “student” had created a Verilog design to do not one round of AES encryption, but every round, all in combinatorial logic with no clocks in between.

Перевод:

этот студент создал Verilog-схему, в которой AES-шифрование выполняется в течение не одного раунда, а каждый раунд, с комбинаторной логикой без тактов.

Имеется в виду, что все операции происходили без разделения на шаги (раунды), в одном раунде. Вот зачем такой перевод? Просто бросили бы ссылку на оригинал.

+1

Книжка «Цифровая схемотехника и архитектура компьютера » от Харрисов как вариант изучения данной темы не подходит?

0

Похоже, что такт — это как скан в ПЛК. Но тогда непонятно, в чем проблемы в объяснениях? Программисты ПЛК легко понимают, что их программа крутится в цикле (ввод-обработка-вывод) и каждый цикл называется скан.

0

Ребят, то, что сейчас прочитаете может оказаться странным/глупым/непонятным, судите как хотите. Заметил, здесь сидят довольно таки умные, толковые люди, кто разбирается во многом по теме.

У меня ситуация наоборот. Нет, не глупый, а лишь не понимаю многие посты здесь. В частности, по коду/разработке ПО.

Всегда были две основне мечты: переехать в США и стать программистом(как звучит-то). Первое сделал. После долгих стараний сейчас нахожусь в округе Seattle(Bellevue, знаете по MS, Amazon, etc.), печатаю находясь в библиотеке колледжа среди разных студентов. Мне 22, родом из города Ташкент, Узбекистан. Но вот желание стать кодером ещё не исполнилось, к сожалению. Изредко бывает захожу на хабру, листаю посты, осознаю, мало что понимаю от них, но есть сильное желание знать, вникнуть. Знаю, есть тонны постов о том, как начать программировать, но хотелось бы услышать ваше мнение. Интерес у меня есть(не знаю, достаточный ли), желание есть, но вот где стартовая линия — не знаю. В колледже Я по «факультету» Software Development, но пока вожусь с начальной математикой, прочими социальными предметами. А хотелось бы начать себя готовить заранее.

Поделитесь любым мнением, своим словом. Буду признателен каждому. Спасибо!

У меня ситуация наоборот. Нет, не глупый, а лишь не понимаю многие посты здесь. В частности, по коду/разработке ПО.

Всегда были две основне мечты: переехать в США и стать программистом(как звучит-то). Первое сделал. После долгих стараний сейчас нахожусь в округе Seattle(Bellevue, знаете по MS, Amazon, etc.), печатаю находясь в библиотеке колледжа среди разных студентов. Мне 22, родом из города Ташкент, Узбекистан. Но вот желание стать кодером ещё не исполнилось, к сожалению. Изредко бывает захожу на хабру, листаю посты, осознаю, мало что понимаю от них, но есть сильное желание знать, вникнуть. Знаю, есть тонны постов о том, как начать программировать, но хотелось бы услышать ваше мнение. Интерес у меня есть(не знаю, достаточный ли), желание есть, но вот где стартовая линия — не знаю. В колледже Я по «факультету» Software Development, но пока вожусь с начальной математикой, прочими социальными предметами. А хотелось бы начать себя готовить заранее.

Поделитесь любым мнением, своим словом. Буду признателен каждому. Спасибо!

-2

Знаю, есть тонны постов о том, как начать программировать, но хотелось бы услышать ваше мнение. Интерес у меня есть(не знаю, достаточный ли), желание есть, но вот где стартовая линия — не знаю.

Просто начните программировать. Найдите себе любую простую задачу и попробуйте ее запрограммировать.

Есть тонны книг о том, как ребенка надо учить ходить, но по факту работает только один способ — ребенок пробует и пробует снова, пока не научится.

0

Сразу видно что статья от программиста к программистам, выявлен какой-то абстрактный подход к разработке цифровой логики на FPGA через магический «такт», паралелизм и циклическую основу всего сущего, такое чувство что у автора нет представления о том, что стоит за всем этим. Такие статьи по большей части могут быть более вредны чем полезны.

А тем кто хочет действительно разрабатывать цифровую логику (и автору в том числе) стоит начать с того чтобы примерить на себя роль инженера и ознакомиться хотябы с такой замечательной книжкой как:

«ЦИФРОВАЯ СХЕМОТЕХНИКА И АРХИТЕКТУРА КОМПЬЮТЕРА»

А тем кто хочет действительно разрабатывать цифровую логику (и автору в том числе) стоит начать с того чтобы примерить на себя роль инженера и ознакомиться хотябы с такой замечательной книжкой как:

«ЦИФРОВАЯ СХЕМОТЕХНИКА И АРХИТЕКТУРА КОМПЬЮТЕРА»

+3

«Программисты CPU -они такие бестактные»

+4

Да, это именно применение языка С++ для разработки проекта ПЛИС. Не для soft процессора.

Вводная статья: здесь

Более подробно на сайте xilinx.com

Компания Xilinx предлагает три продукта:

- Vivado HLS — проектирование отдельных компонентов, является основой для остальных продуктов

- SDSoС — совместная разработка программы и проекта ПЛИС для микросхем серии Zynq (это АРМ+ПЛИС в одном корпусе)

- SDAccel — проектирование проектов ПЛИС с использованием стандарта OpenCL

Всё это уже работает, можно использовать.

Например на GitHub есть проект TCP/IP Stack Design Using Vivado HLS

Собственно из названия уже ясно что это реализация проекта на ПЛИС с использованием Vivado HLS.

+1

Sign up to leave a comment.

Такты для разработчиков