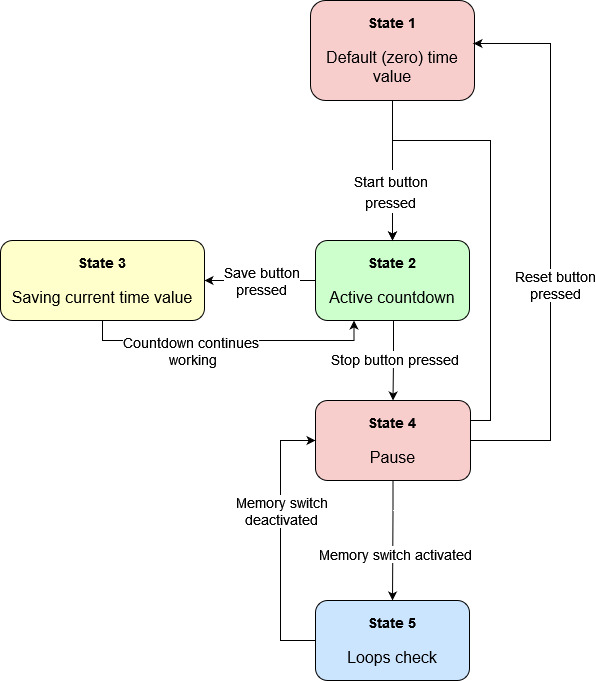

In this report we describe our implementation experience of a stopwatch system executing on an FPGA board. We programmed this device in the Quartus Prime II software environment by using Verilog hardware description language. The program is tailored to the Altera MAX 10 FPGA board, as well as uses a set of other peripheral devices for progress visualization purposes.